wafer.space bare dies and CoB have arrived!

-

wafer.space bare dies and CoB have arrived!

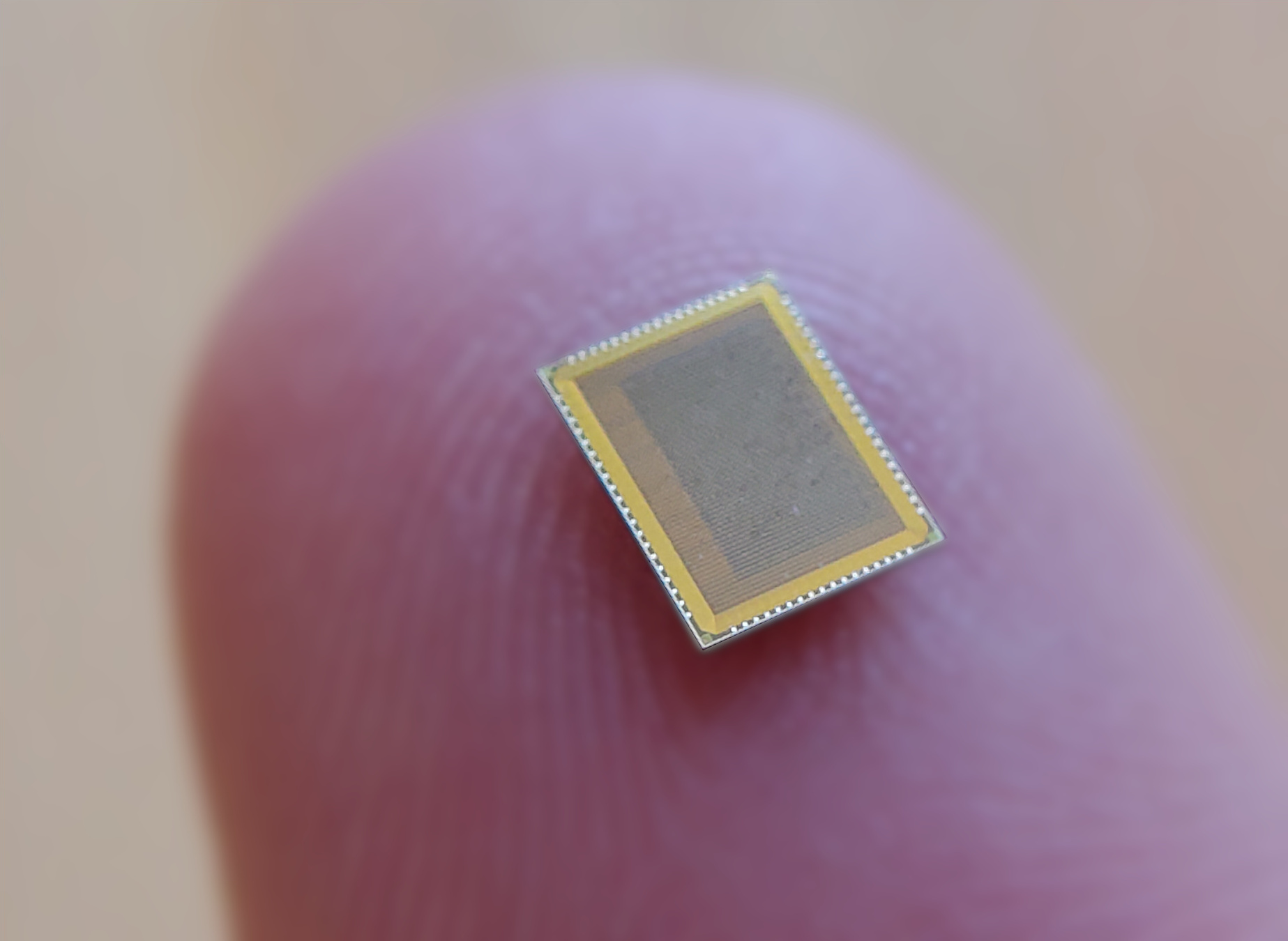

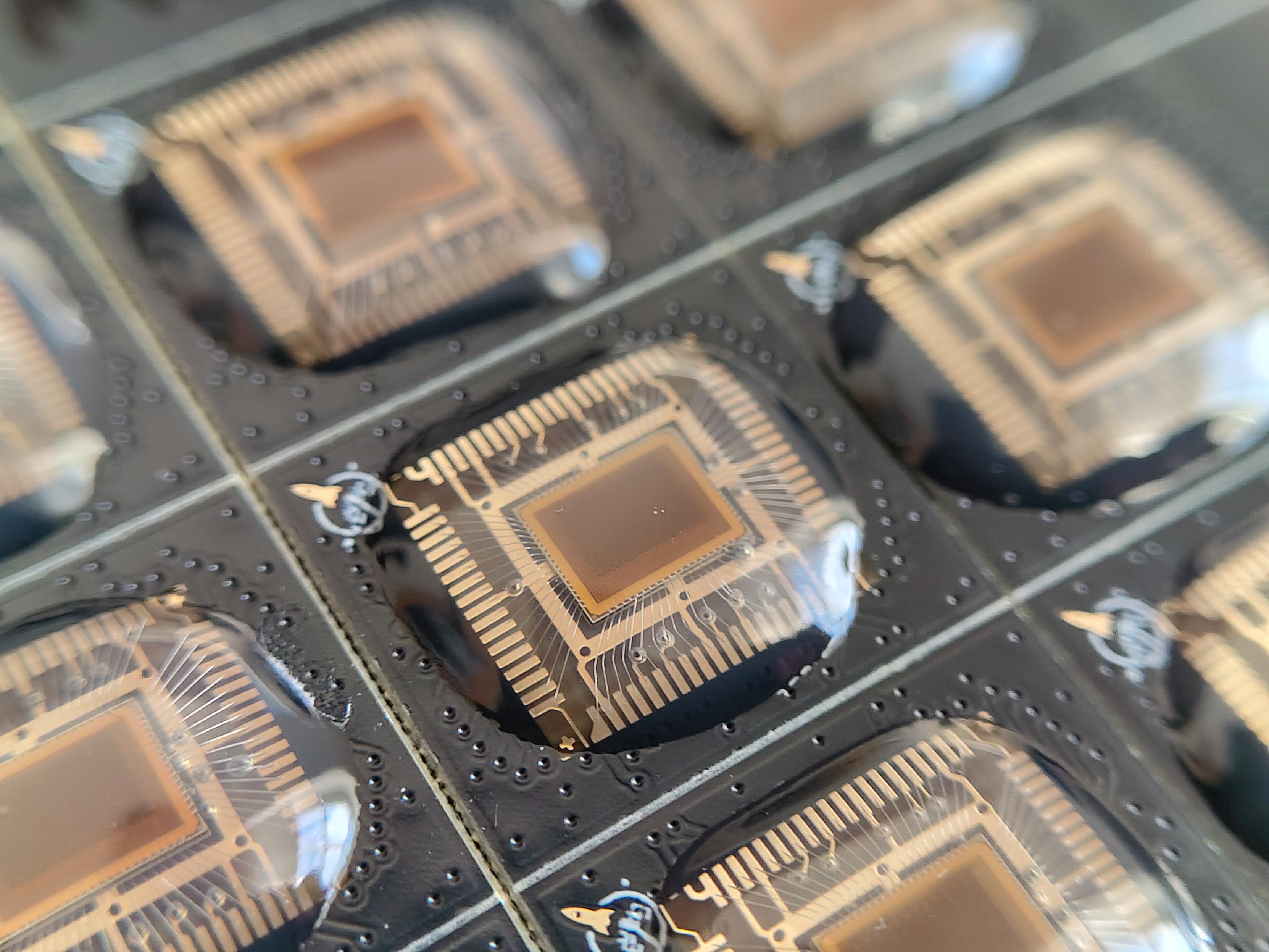

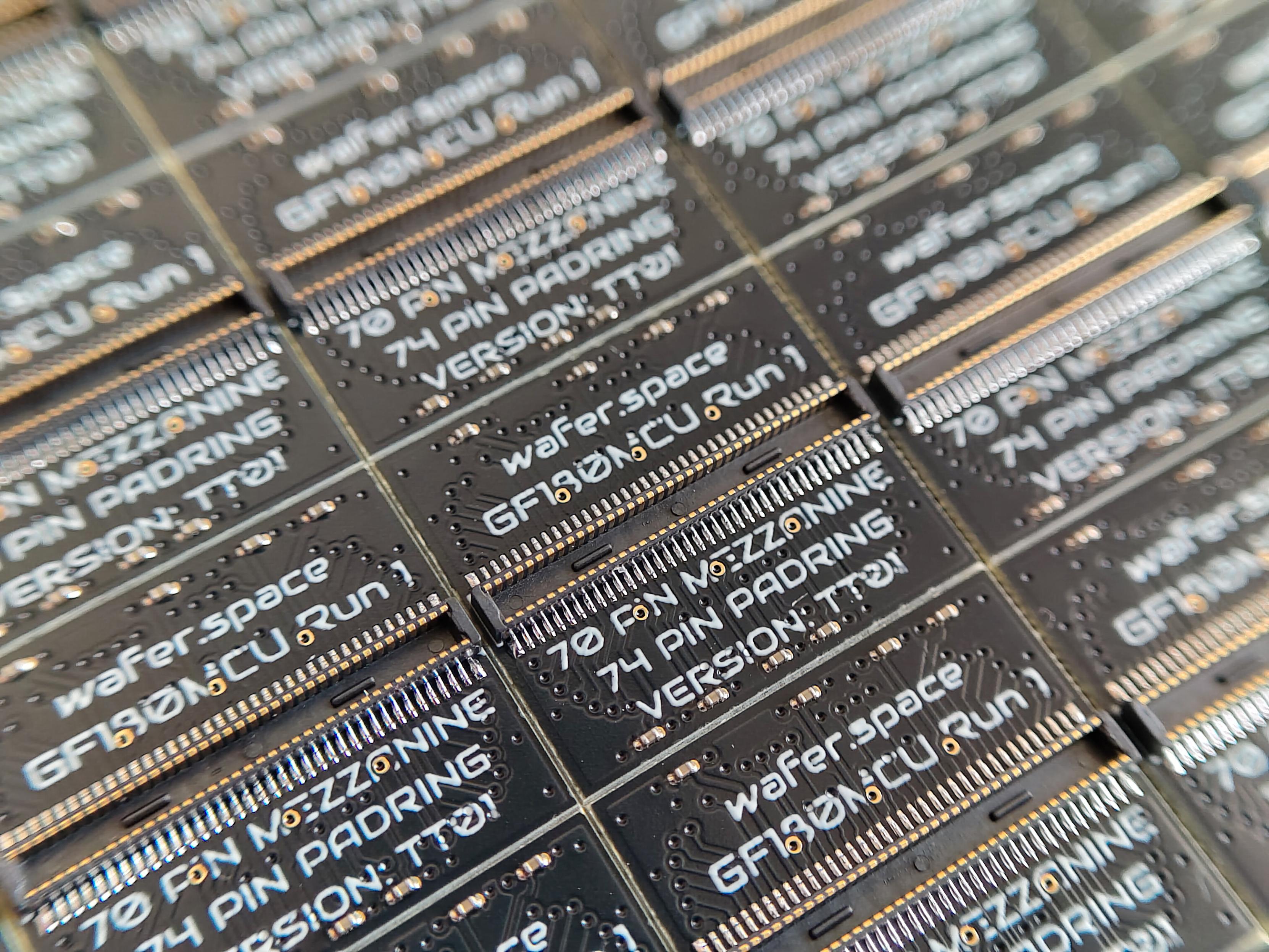

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpga -

wafer.space bare dies and CoB have arrived!

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpgaThe chip was implemented using the wafer.space LibreLane template (https://github.com/wafer-space/gf180mcu-project-template) and uses Yosys and nextpnr for the FPGA toolchain.

You can find all projects from the first wafer.space run here (ID: G801MOLE): https://github.com/wafer-space/ws-run1

-

The chip was implemented using the wafer.space LibreLane template (https://github.com/wafer-space/gf180mcu-project-template) and uses Yosys and nextpnr for the FPGA toolchain.

You can find all projects from the first wafer.space run here (ID: G801MOLE): https://github.com/wafer-space/ws-run1

If you would also like to tape out, registration for the second shuttle run is currently open: https://buy.wafer.space/

-

wafer.space bare dies and CoB have arrived!

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpga@mole99 this is really amazing. How do you know (and specially from where) what exactly to do here in what way for the silicon to work its magic?

I'm also rly. interested to get into silicon circuit designs,, but I'm unsure where to even start.

-

@mole99 this is really amazing. How do you know (and specially from where) what exactly to do here in what way for the silicon to work its magic?

I'm also rly. interested to get into silicon circuit designs,, but I'm unsure where to even start.

@tyalie @mole99 - I recommend getting started with the excellent TinyTapeout.com

If you are the type of person who also benefits from more structure then @matthewvenn 's Zero to ASIC course is also excellent (see https://youtube.com/@ZeroToASICCourse).

-

@tyalie @mole99 - I recommend getting started with the excellent TinyTapeout.com

If you are the type of person who also benefits from more structure then @matthewvenn 's Zero to ASIC course is also excellent (see https://youtube.com/@ZeroToASICCourse).

@mithro @mole99 @matthewvenn ahh thanks. I'll def. take a look through it ^^

-

@mithro @mole99 @matthewvenn ahh thanks. I'll def. take a look through it ^^

@tyalie @mithro @matthewvenn Yes, Tiny Tapeout is ideal if you want to start with ASIC design right away.

As for my personal journey, I started out using the open-source FPGA toolchain (Yosys and nextpnr) with various open-source FPGA boards, such as the excellent iCEBreaker and ULX3S.

I'd recommend learning (System)Verilog or another higher-level HDL that compiles down to it, since Verilog is usually well supported by the open-source tools. -

@tyalie @mithro @matthewvenn Yes, Tiny Tapeout is ideal if you want to start with ASIC design right away.

As for my personal journey, I started out using the open-source FPGA toolchain (Yosys and nextpnr) with various open-source FPGA boards, such as the excellent iCEBreaker and ULX3S.

I'd recommend learning (System)Verilog or another higher-level HDL that compiles down to it, since Verilog is usually well supported by the open-source tools.@tyalie @mithro @matthewvenn You should also familiarize yourself with simulating your design using simulators such as Icarus Verilog or Verilator via cocotb, for example.

The fundamental knowledge you gain from FPGA design can easily be transferred to ASIC design. -

wafer.space bare dies and CoB have arrived!

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpga -

wafer.space bare dies and CoB have arrived!

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpga@mole99 Thank you for such a cool contribution to open tech!

-

wafer.space bare dies and CoB have arrived!

These are from my open-source FABulous FPGA, which was part of the first shuttle run.

It's a small FPGA with 480x LC, 6x MAC, 12x register files and 6x SRAM. The source files are available in the repository: https://github.com/mole99/gf180mcu-fabulous-fpga@mole99 smol! ^~^

is a cute lil chip -

@mole99 smol! ^~^

is a cute lil chip@mole99 saw the die pic and brain immediately went "me want bite"

me nomming the forbidden stroopwafel

me nomming the forbidden stroopwafel -

R relay@relay.mycrowd.ca shared this topic