And another chip submitted for tapeout - HeiChips 🎉

-

And another chip submitted for tapeout - HeiChips

This one has been in the works for some time, but since the shuttle was canceled last fall, it was postponed to a later one.

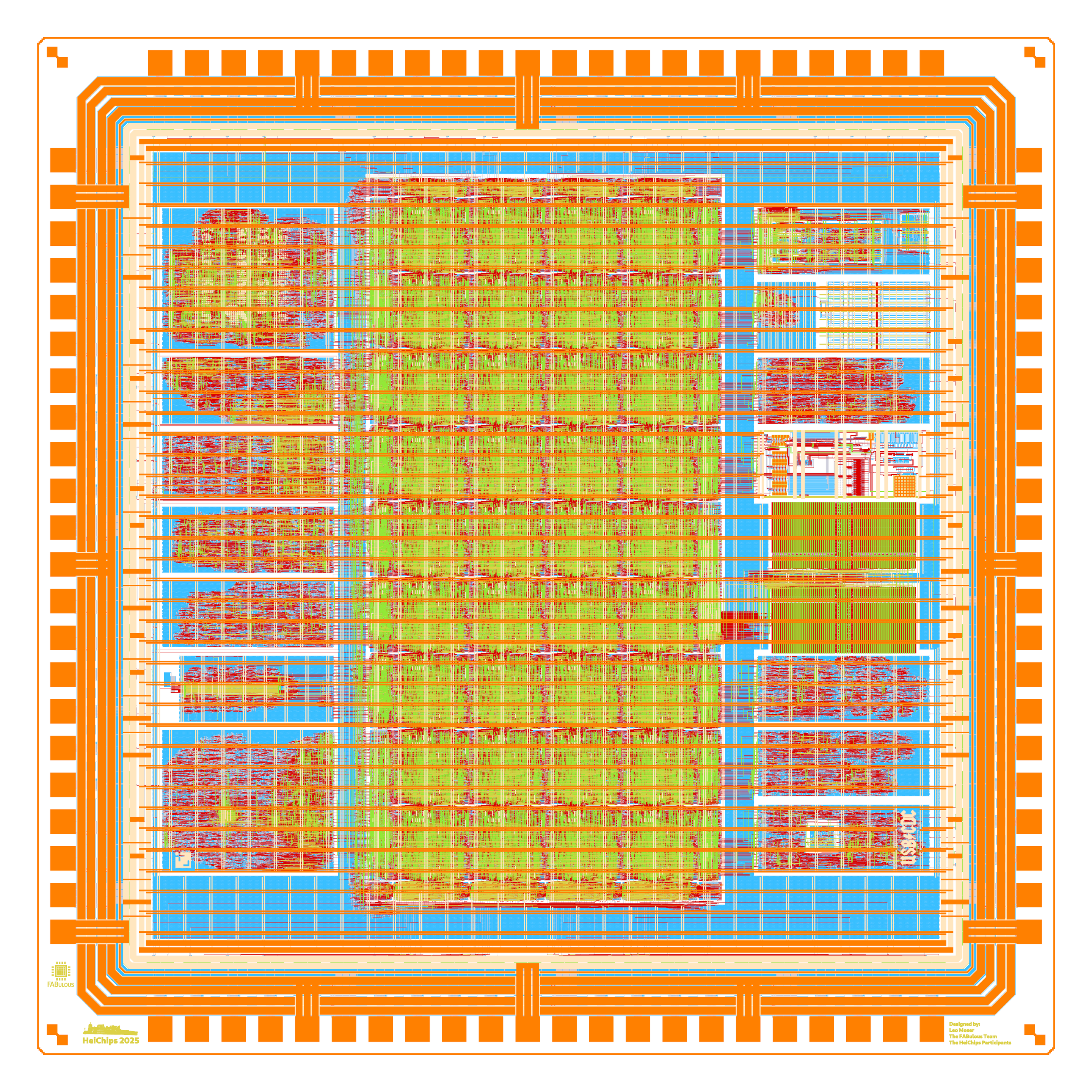

It's an open-source chip featuring user projects created by participants of the HeiChips Summer School 2025 (https://heichips.github.io/). How cool is that?

The chip uses 9mm² of silicon on SG13CMOS and has been submitted to IHP's Low-Cost MPW shuttle (https://dk.ihp-microelectronics.com/OpenSourceRequest.php).More below

️

️ -

And another chip submitted for tapeout - HeiChips

This one has been in the works for some time, but since the shuttle was canceled last fall, it was postponed to a later one.

It's an open-source chip featuring user projects created by participants of the HeiChips Summer School 2025 (https://heichips.github.io/). How cool is that?

The chip uses 9mm² of silicon on SG13CMOS and has been submitted to IHP's Low-Cost MPW shuttle (https://dk.ihp-microelectronics.com/OpenSourceRequest.php).More below

️

️The stats are: 14 user projects, two of which are large slots and four of which are analog/mixed-signal designs.

At the center is a reprogrammable FPGA fabric that connects all the user projects, the I/Os, and the SRAM. -

The stats are: 14 user projects, two of which are large slots and four of which are analog/mixed-signal designs.

At the center is a reprogrammable FPGA fabric that connects all the user projects, the I/Os, and the SRAM.HeiChips includes a variety of incredible user projects, among them: two different RISC-V cores, an 8-bit CPU, waveform + tone generation, a USB CDC core, a systolic array (4x4 matrices), a cryo DAC, an experimental 10 Mbps Ethernet PHY, analog standard cells and floating-gate structures, and many more!

For more information about the chip and the user projects, check out the tapeout repository: https://github.com/FPGA-Research/heichips25-tapeout

-

HeiChips includes a variety of incredible user projects, among them: two different RISC-V cores, an 8-bit CPU, waveform + tone generation, a USB CDC core, a systolic array (4x4 matrices), a cryo DAC, an experimental 10 Mbps Ethernet PHY, analog standard cells and floating-gate structures, and many more!

For more information about the chip and the user projects, check out the tapeout repository: https://github.com/FPGA-Research/heichips25-tapeout

To test a user project, first upload a bitstream to the FPGA which selects the project and connects it to the I/Os and SRAM as required. The bitstream is created using Yosys and nextpnr - a complete open-source FPGA toolchain.

-

To test a user project, first upload a bitstream to the FPGA which selects the project and connects it to the I/Os and SRAM as required. The bitstream is created using Yosys and nextpnr - a complete open-source FPGA toolchain.

I'm incredibly happy to have worked on this chip! It utilizes LibreLane 3.0 (https://librelane.org) and its latest features, such as automated analog routing through non-default rules. The complete, tapeout-ready chip can be generated with just one command.

Thanks to everyone involved and for the support by Heidelberg University, BMFTR (the German Federal Ministry of Research, Technology and Space) and Chipdesign Germany for making HeiChips possible. Thank you!

-

I'm incredibly happy to have worked on this chip! It utilizes LibreLane 3.0 (https://librelane.org) and its latest features, such as automated analog routing through non-default rules. The complete, tapeout-ready chip can be generated with just one command.

Thanks to everyone involved and for the support by Heidelberg University, BMFTR (the German Federal Ministry of Research, Technology and Space) and Chipdesign Germany for making HeiChips possible. Thank you!

Here are some further links:

Tapeout repository: https://github.com/FPGA-Research/heichips25-tapeout

LibreLane: https://librelane.org/

IHP Open PDK: https://github.com/IHP-GmbH/IHP-Open-PDK

FABulous: https://github.com/FPGA-Research/FABulous -

R relay@relay.infosec.exchange shared this topic on