Some people claim thar the 6502 is a RISC processor.

-

@etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen Yeh I may be misremembering, to be honest, long time ago.

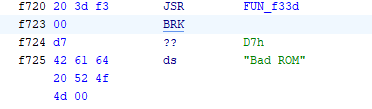

@revk @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen By default on the Acorn 8-bit OS, the IRQ/BRK vector (0xfffe) redirects into ROM, which then splits it depending on the I flag.

If it is a BRK, then it will pull the calling address from stack and store the following address in 0x00ED and 0x00FE and then jump to the code pointed to by 0x0202. By default this will print the null terminated ASCII message after the BRK.

For example:

-

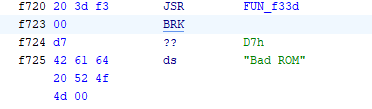

@revk @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen By default on the Acorn 8-bit OS, the IRQ/BRK vector (0xfffe) redirects into ROM, which then splits it depending on the I flag.

If it is a BRK, then it will pull the calling address from stack and store the following address in 0x00ED and 0x00FE and then jump to the code pointed to by 0x0202. By default this will print the null terminated ASCII message after the BRK.

For example:

@revk @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen

There is a warning in the Advanced User guide about using this for anything complex:

"Note that although a fully prepared exit from a BRK instruction

is possible, neither the operating system or BASIC expect a

return from this vector. Possibly fatal results may occur if such

a return is made as paged ROM software typically stores the

BRK, error number and message in page one below the stack,

returning there is very hazardous. The exception to this is when

using the BRK instruction as a breakpoint in user supplied

machine code, and is not used as a standard error generating

mechanism." -

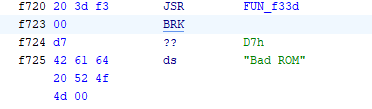

@revk @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen By default on the Acorn 8-bit OS, the IRQ/BRK vector (0xfffe) redirects into ROM, which then splits it depending on the I flag.

If it is a BRK, then it will pull the calling address from stack and store the following address in 0x00ED and 0x00FE and then jump to the code pointed to by 0x0202. By default this will print the null terminated ASCII message after the BRK.

For example:

@tautology @revk @etchedpixels @simonzerafa @brouhaha @phloggen What causes a "Bad ROM"? Is that what you get if you pull the BASIC ROM out?

-

The DG Nova was the first RISC, and anybody who wants to argue otherwise must bring an architecture with less than 18 instructions to the debate.

@phloggen @brouhaha Hmm less than 18; Manchester Baby 1948 - 7 instructions; https://en.wikipedia.org/wiki/Manchester_Baby#Programming

-

@revk @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen

There is a warning in the Advanced User guide about using this for anything complex:

"Note that although a fully prepared exit from a BRK instruction

is possible, neither the operating system or BASIC expect a

return from this vector. Possibly fatal results may occur if such

a return is made as paged ROM software typically stores the

BRK, error number and message in page one below the stack,

returning there is very hazardous. The exception to this is when

using the BRK instruction as a breakpoint in user supplied

machine code, and is not used as a standard error generating

mechanism."@tautology @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen The paged ROMs were fun. I have one application that actually took up two slots with calls between them - all good fun.

-

@tautology @etchedpixels @simonzerafa @kbm0 @brouhaha @phloggen The paged ROMs were fun. I have one application that actually took up two slots with calls between them - all good fun.

@revk @tautology @etchedpixels @simonzerafa @brouhaha @phloggen You could make a cheap "sideways RAM" board with static RAM mapped into the ROM slots.

-

@revk @tautology @etchedpixels @simonzerafa @brouhaha @phloggen You could make a cheap "sideways RAM" board with static RAM mapped into the ROM slots.

@revk @tautology @etchedpixels @simonzerafa @brouhaha @phloggen I seem to remember there was a romsel header on the BBC B that could address up to 16 ROMs. You had to steal the R/W line from somewhere else on the board.

-

The DG Nova was the first RISC, and anybody who wants to argue otherwise must bring an architecture with less than 18 instructions to the debate.

-

@tautology @revk @etchedpixels @simonzerafa @brouhaha @phloggen What causes a "Bad ROM"? Is that what you get if you pull the BASIC ROM out?

@kbm0 @revk @etchedpixels @simonzerafa @brouhaha @phloggen that code was in the middle of the ROMFS code (where it treats a ROM like a virtual tape), and the code before it looks for valid codes for a tape file header, so it's the error when you try and use ROMFS on a non-ROMFS ROM.

-

@kbm0 @revk @etchedpixels @simonzerafa @brouhaha @phloggen that code was in the middle of the ROMFS code (where it treats a ROM like a virtual tape), and the code before it looks for valid codes for a tape file header, so it's the error when you try and use ROMFS on a non-ROMFS ROM.

@tautology @revk @etchedpixels @simonzerafa @brouhaha @phloggen Not sure I ever encountered a ROMFS ROM in anger... I remember there was that whole thing with speech "phROMs" and that mysterious cutout on the LHS of the keyboard that nobody ever used. Features mandated by the educational spec of the Beeb micro I expect.

-

The DG Nova was the first RISC, and anybody who wants to argue otherwise must bring an architecture with less than 18 instructions to the debate.

-

@tautology @revk @etchedpixels @simonzerafa @brouhaha @phloggen Not sure I ever encountered a ROMFS ROM in anger... I remember there was that whole thing with speech "phROMs" and that mysterious cutout on the LHS of the keyboard that nobody ever used. Features mandated by the educational spec of the Beeb micro I expect.

@kbm0 @revk @etchedpixels @simonzerafa @brouhaha @phloggen some of the Acornsoft releases on the Electron / Master used ROMFS as it made it really quick to convert a BASIC tape to a plug in ROM.

-

@revk @etchedpixels @kbm0 @brouhaha @phloggen

It's been possible through, dark arts and necromancy, to add a protected mode to the Z80, which would have been very cool in 1989

GitHub - Andy18650/HEC-Model-Z1: A Z80 computer with protected mode support

A Z80 computer with protected mode support. Contribute to Andy18650/HEC-Model-Z1 development by creating an account on GitHub.

GitHub (github.com)

@simonzerafa @revk @etchedpixels @kbm0 @phloggen

You can add a "protected mode" by adding additional logic to any processor. It was done in 1982 or so by Motorola for the MC6809, by way of the MC6829 MMU chip, which of course also added memory mapping. The MC6829 could also be used by other microprocessors with a synchronous bus, including the 6502.

1/ -

@simonzerafa @etchedpixels @kbm0 @brouhaha @phloggen 6502 BRK was uses creatively by BBC Micro as I recall.

@revk @simonzerafa @etchedpixels @kbm0 @brouhaha @phloggen Best use of BRK is in the Atari 2600 F1 racing game where the fact that it pushes 3 items onto the stack in one instruction is used to to perform 3 distinct sprite operations in one go, drawing the left and right side of the race track in the distance that would otherwise be too close to represent as distinct operations.

-

@simonzerafa @revk @etchedpixels @kbm0 @phloggen

You can add a "protected mode" by adding additional logic to any processor. It was done in 1982 or so by Motorola for the MC6809, by way of the MC6829 MMU chip, which of course also added memory mapping. The MC6829 could also be used by other microprocessors with a synchronous bus, including the 6502.

1/@brouhaha @simonzerafa @revk @kbm0 @phloggen The 6829 is not a protected mode in any real sense and the 6809 isn't capable of doing a protected mode because like the 6502 there are instructions that hard crash the processor.

The 6309 is capable with a lot of care of doing so but even then it's fairly hairy as you don't have a separate supervisor stack pointer. -

@simonzerafa @revk @etchedpixels @kbm0 @phloggen

You can add a "protected mode" by adding additional logic to any processor. It was done in 1982 or so by Motorola for the MC6809, by way of the MC6829 MMU chip, which of course also added memory mapping. The MC6829 could also be used by other microprocessors with a synchronous bus, including the 6502.

1/@simonzerafa @revk @etchedpixels @kbm0 @phloggen

Precedent for this sort of thing goes back to the IBM 709 computer, a vacuum tube machine introduced in 1957. MIT added a protected mode for use by their CTSS operating system (Compatible Time Sharing System), the first general-purpose computer time-sharing system, operational in 1961. -

@revk @simonzerafa @kbm0 @brouhaha @phloggen carry flag always gets me on 6502 when switching the CPU I am working with 6800 series, 8080 series and most others it's the other way around on subtract

@etchedpixels @revk @simonzerafa @kbm0 @phloggen

And just due to my having some more 6502 programming early on, I'm used to the carry/not borrow of the 6502, and get tripped up by other processors that have carry/borrow. -

@phloggen @brouhaha Hmm less than 18; Manchester Baby 1948 - 7 instructions; https://en.wikipedia.org/wiki/Manchester_Baby#Programming

@penguin42 @phloggen

That's the SSEM I.mentioned. -

@etchedpixels @revk @simonzerafa @kbm0 @phloggen

And just due to my having some more 6502 programming early on, I'm used to the carry/not borrow of the 6502, and get tripped up by other processors that have carry/borrow.@brouhaha @etchedpixels @revk @kbm0 @phloggen

Binary Coded Decimal (BCD) mode for arithmetic was always a fun activity on the 6502

-

@larsbrinkhoff @phloggen

IIRC, that was a part of the original definition, but the industry has clearly moved past it.