i've been doing a deep dive into SPI NOR flash command set and it is horrifying.

-

@r those did not have 50 different ways to clock bits over four pins and also built-in ECC and so on

-

i've been doing a deep dive into SPI NOR flash command set and it is horrifying. i don't know how anything works. none of these devices agree with each other on anything, even devices from the same family of the same vendor with the "same" part number (but suffix J instead of suffix V or whatever)

@whitequark They’re all a total nightmare, and it’s hard to find a subset to even bootstrap things enough to read the first 512 bytes, where vendors tend to stash a list of NOR quirks. The worst are devices where you can flash their config page to never be compatible with the standard set, persistently.

-

@whitequark They’re all a total nightmare, and it’s hard to find a subset to even bootstrap things enough to read the first 512 bytes, where vendors tend to stash a list of NOR quirks. The worst are devices where you can flash their config page to never be compatible with the standard set, persistently.

@jripley hm, sorry I meant SPI ones, those do at least have the SFDP

-

note how there are two commands to read status registers 1 & 2, but only one command to write them both. why? well

most devices do have a command to write status register 2 exclusively. but some devices reset status register 2 if you write status register 1, and some of them do not

(since then they've added a status register 3)

@whitequark I keep not understanding why silicon houses have write-only registers with no shadow and no capability of idempotent operations.

-

note how there are two commands to read status registers 1 & 2, but only one command to write them both. why? well

most devices do have a command to write status register 2 exclusively. but some devices reset status register 2 if you write status register 1, and some of them do not

(since then they've added a status register 3)

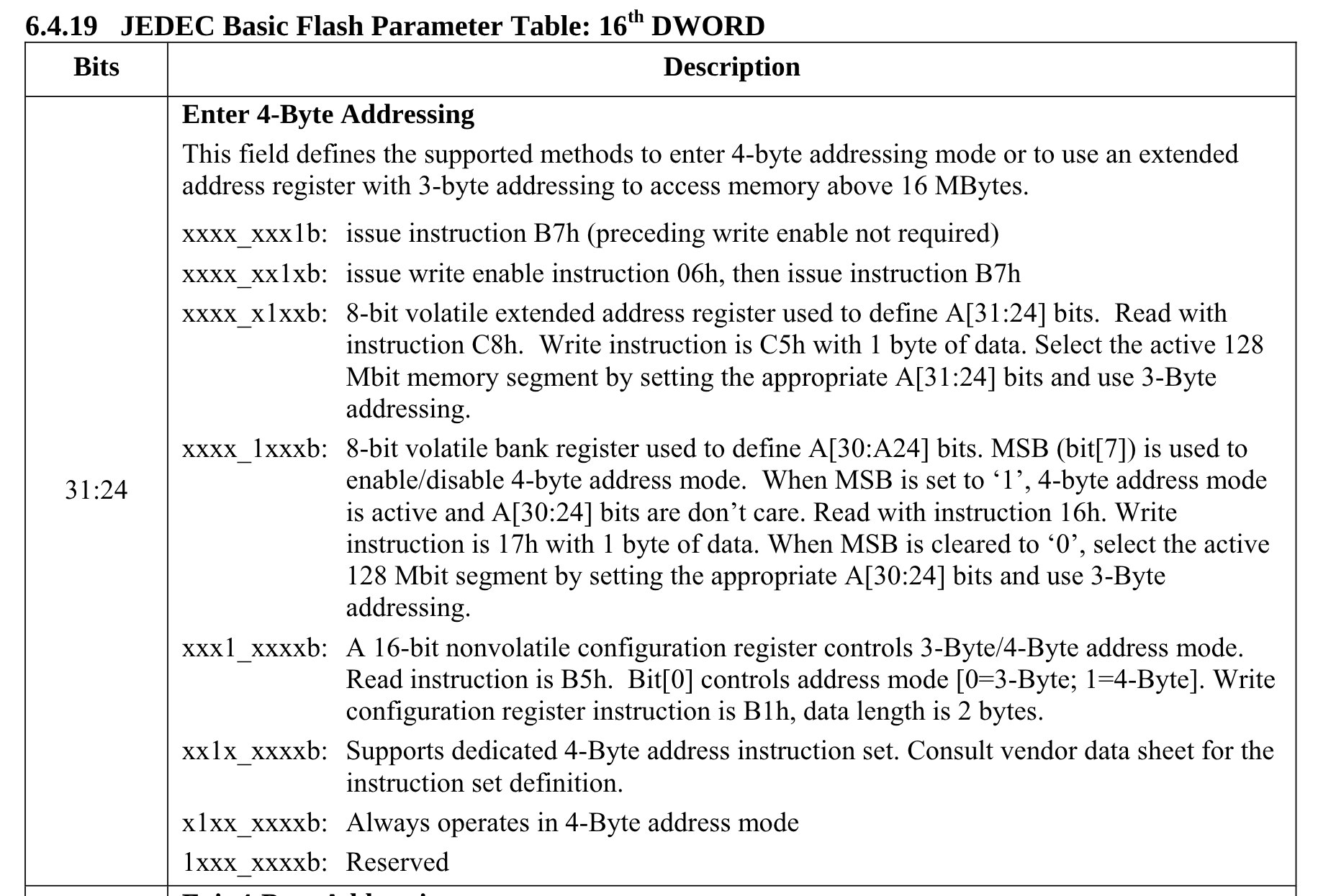

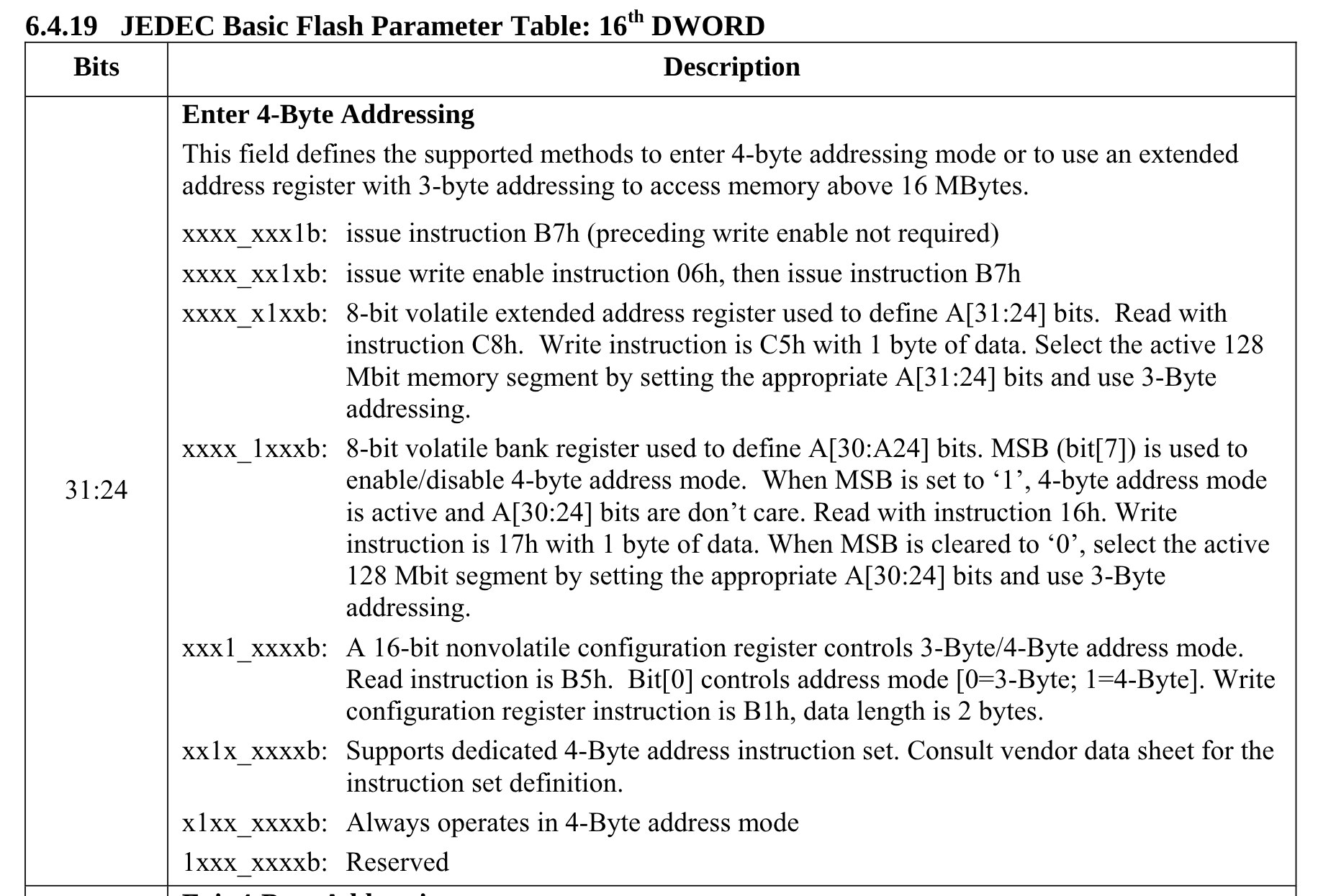

behold: crackhead technology

data storage devices terrify me. the only way to store anything is to keep like five different copies of it on mediums made by different vendors. and even then i don't trust it

-

@whitequark I keep not understanding why silicon houses have write-only registers with no shadow and no capability of idempotent operations.

@doomsey these are not write-only, the instruction set is just designed by a crackhead

-

behold: crackhead technology

data storage devices terrify me. the only way to store anything is to keep like five different copies of it on mediums made by different vendors. and even then i don't trust it

@whitequark as a person mostly dealing with web based crackheadedness, and an absolute fear of anything hardware related, these threads where I understand absolutely nothing are fascinating and terrifying.

-

i've been doing a deep dive into SPI NOR flash command set and it is horrifying. i don't know how anything works. none of these devices agree with each other on anything, even devices from the same family of the same vendor with the "same" part number (but suffix J instead of suffix V or whatever)

@whitequark We're fortunate at the office that no one expects us to swap from one to another without software changes, so we can get away with writing to the chosen device.

-

there is a standard, JESD216B (unless they released JESD216C already) and it does a surprisingly good job at reining in the crackheadedness of it all, but you do end up with 60 pages of... this

@whitequark Somehow, they are up to JESD216H. It doesn't get any better.

Would have been nice if there had been a standard for the SPI flash itself rather than just the SFDP data.

-

@doomsey these are not write-only, the instruction set is just designed by a crackhead

@whitequark fortunately we have an incompetent offshore team so I don't have to look at that particular brokenness until it's too late

-

@whitequark Somehow, they are up to JESD216H. It doesn't get any better.

Would have been nice if there had been a standard for the SPI flash itself rather than just the SFDP data.

@whitequark JSED216H is 191 pages. Almost like the manufacturers do as they please designing the commands for these things, not communicating with one another, JEDEC just adds it all to JESD216.

JESD216H (August 2025), JESD216G (November 2024), JESD216F.02 (June 2022), JESD216F.01 (February 2022), JESD216F (December 2021), JESD216E (August 2021), JESD216D (August 2019), JESD216C (August 2018), JESD216B (May 2014), JESD216A (July 2013), and JESD216 (April 2011).

-

R relay@relay.infosec.exchange shared this topic